# Explorando a Assimetria do Dimensionamento de Transistores CMOS em Portas Complexas

Vítor de M. Mandowski<sup>1</sup>, Henrique C. Kessler<sup>1</sup>, Leomar S. da Rosa Júnior<sup>1</sup>

<sup>1</sup>Centro de Desenvolvimento Tecnológico

Universidade Federal de Pelotas (UFPel)

Pelotas – RS – Brasil

**Abstract.** *To efficiently design logic gates, it is crucial to size the transistors appropriately to optimize area, propagation delay, and power consumption. There are widely used techniques in the literature for transistor sizing, but it is believed that an alternative sizing approach may offer better results for complex gates. In this context, this study explored asymmetric transistor sizing in complex gates, resulting in improvements in propagation delay for logic gates with large output loads.*

**Resumo.** *Para projetar portas lógicas com eficiência, é crucial dimensionar os transistores adequadamente, buscando otimizar área, atraso de propagação e consumo de potência. Para dimensionar os transistores, existem na literatura técnicas amplamente utilizadas, contudo, acredita-se que um modelo alternativo de dimensionamento possa oferecer melhores resultados para as portas complexas. Neste contexto, o presente trabalho explorou um dimensionamento assimétrico de transistores em portas complexas, resultando em ganhos no atraso de propagação em portas lógicas com grandes cargas de saída.*

## 1. Introdução

O desempenho de um circuito integrado depende diretamente da qualidade do projeto das portas lógicas utilizadas. O número de transistores em um chip cresce de modo exponencial concomitantemente à sua complexidade [Moore 1965], a biblioteca de células torna o projeto factível, visto que os fabricantes disponibilizam um conjunto de células previamente projetadas e otimizadas. No entanto, essa vantagem também torna-se uma restrição, pois limita a capacidade de otimização do circuito, por ser limitado à biblioteca de células.

Caso um projetista queira otimizar o seu circuito criando sua própria porta lógica, ele pode optar em usar portas lógicas complexas. As portas lógicas complexas podem executar funções lógicas mais sofisticadas, contudo, essas portas lógicas não se encontram presentes nas bibliotecas de células. O motivo de não existir um fluxo de projeto de portas complexas, é o elevado grau de complexidade de leiaute e o desconhecimento de seu nicho de utilização.

O dimensionamento é responsável pelas características elétricas do transistor, e este, é dinâmico de acordo com a característica do pulso de entrada na porta lógica e também sua carga de saída. Dito isso, em uma biblioteca de células, existem portas lógicas com dimensionamentos variados para garantir que exista uma porta com comportamento elétrico satisfatório para todas as situações. A carga de saída determina a quantidade de

corrente elétrica que o transistor precisa conduzir, sendo assim, cargas maiores precisam de um maior dimensionamento, para que não se tenha um maior atraso.

Com a função de alcançar um equilíbrio de atraso entre os caminhos das redes de transistores, existe a técnica de dimensionamento baseada no *Logical Effort* (Esforço Lógico) [Sutherland et al. 1999]. O objetivo deste trabalho é propor uma abordagem alternativa de dimensionamento que seja projetada baseada nas portas complexas, visando uma melhor performance de atraso, consumo ou área para as mesmas.

## 2. Contexto da Área de Microeletrônica

A tecnologia CMOS (*Complementary Metal-Oxide-Semiconductor*) representa o ápice da evolução na área de circuitos integrados [Kofuji et al. 1990]. Ela é amplamente reconhecida por sua versatilidade e eficiência, sendo uma escolha dominante na fabricação de dispositivos eletrônicos modernos. O princípio fundamental do CMOS envolve o uso de pares de transistores MOSFET (*Metal-Oxide-Semiconductor Field-Effect Transistor*), um P-MOSFET e um N-MOSFET, que operam de forma complementar. Isso permite que os dispositivos CMOS tenham uma grande redução de energia quando estão em repouso, tornando-os ideais para circuitos de baixa potência, como os encontrados em dispositivos portáteis e sensores.

A caracterização elétrica é um procedimento essencial no projeto de circuitos integrados, envolvendo a medição e análise minuciosa dos comportamentos elétricos das redes de transistores que compõem esses dispositivos, frequentemente realizada através de simulações elétricas avançadas. Existem três métricas fundamentais para otimizar um circuito com base em sua caracterização, sendo elas o atraso de resposta do sistema, o consumo de potência e a área ocupada pelo circuito [Weste and Harris 2011].

O atraso é um fator crucial que determina a frequência máxima de operação, enquanto o consumo de potência determina a quantidade de energia que o circuito irá dissipar, o que é essencial para dispositivos móveis. Além disso, é essencial considerar a área que o circuito ocupará, tendo em vista que essa está diretamente relacionada ao custo do circuito. Idealmente, deve-se encontrar um equilíbrio entre essas características, podendo priorizar alguma delas dependendo da aplicação do circuito. Por exemplo, pode-se ter um circuito que precise ser extremamente rápido ou outro que não possa consumir muita energia.

As portas lógicas desempenham um papel crucial na eletrônica digital, uma vez que formam a base para a construção de circuitos mais complexos, permitindo o processamento e a manipulação de informações binárias de maneira eficaz. Elas são compostas por redes de transistores que operam de acordo com os princípios da álgebra booleana, realizando operações fundamentais como a negação (NOT), disjunção (OR) e conjunção (AND) em sinais elétricos. Essas operações são essenciais para a execução de tarefas lógicas e aritméticas nos dispositivos eletrônicos modernos.

As bibliotecas de células contêm as principais portas lógicas otimizadas para atraso, consumo e área. Uma biblioteca de células é caracterizada eletricamente para fornecer os dados necessários para a síntese lógica sobre como o circuito se comportará, sem a necessidade de simulação elétrica. O formato padrão para a caracterização de uma biblioteca de células é o *Liberty*. O *Liberty* é um formato de arquivo que possui um con-

junto de regras para caracterizar circuitos integrados, descrevendo as características de temporização e consumo de energia das células padrão.

Devido à complexidade envolvida na criação de uma biblioteca de células, geralmente busca-se sua generalização para atender a diversos circuitos. Uma biblioteca de células bem projetada é otimizada para uso em vários circuitos [Ricci et al. 2007]. No entanto, apesar de ser implementada com portas lógicas simples, acredita-se que seja possível obter ganhos em situações específicas com portas complexas [Kessler 2022] e [Marques et al. 2007].

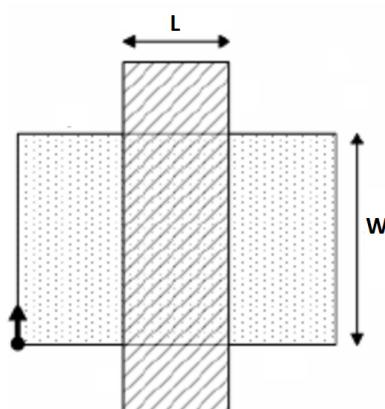

Para compreender o conceito de dimensionamento, é necessário entender que um transistor é composto por um comprimento de canal “L”, definido pela tecnologia do transistor, e uma largura “W”. Esta última é a variável que pode ser dimensionada, como mostrado na Figura 1. Quanto maior a largura do transistor, maior será a capacidade de condução, resultando em uma redução do atraso da porta (até atingir a saturação). No entanto, aumentar a largura implica em um aumento da área ocupada pelo transistor e consumo de potência. Embora o aumento das dimensões também aumente a dissipação de energia e o custo da área, isso pode se tornar necessário quando os transistores estão em série. Devido ao sinal ter que percorrer um caminho lógico mais longo, o atraso pode ser impactado, levando ao desempenho insatisfatório da porta lógica. Nesse contexto, o dimensionamento ajusta as características elétricas, permitindo adequar o circuito as especificações do projeto.

**Figura 1. Medidas de um transistor. Adaptado de: [Tseng et al. 2005].**

### 3. Trabalhos Relacionados

Para realizar o dimensionamento, existem técnicas de dimensionamento, como por exemplo a técnica baseada no *Logical Effort* [Sutherland et al. 1999] que será referenciada neste trabalho como “LE”. O *Logical Effort* consiste em uma abordagem para estimar o atraso de propagação de um circuito. Para isso, é necessário aumentar as dimensões dos transistores de uma porta lógica com base na quantidade de transistores em série entre a alimentação (PMOS ou NMOS) e o nó de saída do transistor. Por exemplo, considerando uma porta lógica com dimensionamento “W” e um caminho em que três transistores estão em série, estes transistores teriam um dimensionamento três vezes maior que “W”. Embora essa técnica seja bastante eficaz para portas lógicas simples, pode não ser tão adequada para portas complexas, conforme [Kessler et al. 2022a] e [Böhlke 2021].

As portas complexas são construídas a partir da associação de vários transistores, gerando uma grande porta lógica, em uma configuração que permite a implementação de funções lógicas específicas. Essas portas lógicas contêm mais transistores do que as portas lógicas simples, resultando em mais caminhos entre a alimentação e a saída. O caminho crítico do circuito é definido pelo caminho entre a alimentação e a saída com o maior atraso. Nesse contexto, o LE pode não ser tão eficaz em uma rede de transistores com bifurcações, uma vez que o atraso será definido pelo caminho crítico do circuito. Aplicar o LE em alguns casos de caminhos bifurcados pode aumentar a área e o consumo de potência do circuito sem resultar em ganhos de atraso.

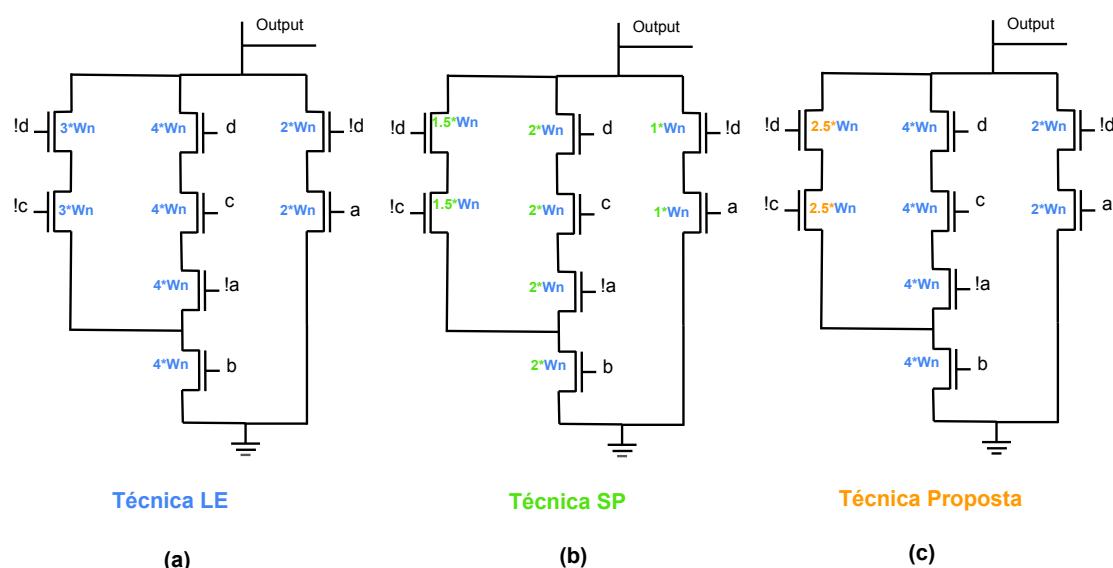

O LE [Sutherland et al. 1999] é uma técnica que dimensiona um transistor de forma simétrica, ou seja, para quaisquer transistor presente no caminho “X” entre alimentação e saída, o transistor será dimensionado como “X”, diferente de um modelo assimétrico, o qual dimensionaria como “Y” um transistor do caminho “X”. O LE multiplica o “W” pela quantidade de transistores em série existentes no caminho do transistor. Uma abordagem de dimensionamento diferente do LE pode ser mais adequada para portas complexas, como por exemplo, existe uma técnica adaptada do LE focada em portas complexas, a qual inclui um fator de multiplicação série (S) e paralelo (P) para dimensionar os transistores juntamente com o LE [Böhlke 2021]. Para referência ao longo deste trabalho, denominaremos essa técnica como “Técnica SP”.

A técnica SP envolveu a simulação elétrica de múltiplas portas lógicas complexas, utilizando como base o conceito de LE e explorando variações nos fatores de série e paralelo. Após realizar extensivas simulações, observou-se consistentemente que, em muitos casos, os resultados mais favoráveis foram obtidos quando o fator paralelo era definido como uma vez o LE, e o fator série como 0.5 vezes o LE. Verificou-se que ao reduzir pela metade o LE, não ocorriam perdas significativas no atraso de propagação em portas lógicas complexas. Esta constatação permitiu a otimização da área ocupada, resultando em ganhos substanciais de consumo de potência. Neste contexto, a estratégia de ajustar os fatores série e paralelo proporcionou uma abordagem eficaz para a redução de área e o aprimoramento do consumo de energia em circuitos complexos.

Dado que os caminhos críticos determinam o atraso de um circuito, o objetivo do dimensionamento assimétrico é reduzir a dimensão de transistores que não fazem parte do caminho crítico, visando ganhos em potência sem prejudicar o atraso. Esta abordagem assimétrica envolve aplicar o fator de multiplicação diferente do LE ou da técnica SP de dimensionamento aos caminhos não críticos do circuito. Para realizar o cálculo da técnica proposta, partiu-se da premissa de que o caminho lógico com o maior número de transistores determina o atraso crítico da porta lógica. Deste modo, é possível modificar caminhos que apresentem bifurcações, visando compensar o valor “W” dos transistores.

Considerando dois caminhos: um com 4 transistores, sendo este o caminho crítico, e outro com 3 transistores, ambos compartilhando um transistor em comum. Através da abordagem do LE, cria-se um caminho com um transistor de 4 vezes o “W” e dois transistores de 3 vezes “W” totalizando 10 vezes o “W” neste caminho. No entanto, acredita-se que para compensar esse caminho, é necessário apenas um valor de 9 vezes o “W” (3 vezes em cada transistor). Assim, podemos ajustar os dois transistores de 3 vezes o “W” para 2.5 vezes, resultando em um caminho equivalente com um total de 9 vezes o “W” para os três transistores. Esse ajuste é essencial, uma vez que o transistor com 4

vezes o “W” não pode ser alterado, pois pertence ao caminho crítico com 4 transistores. Portanto, supõe-se ser possível reduzir a área dos transistores de 3 vezes o “W” para 2.5 vezes, mantendo a compensação para evitar torná-lo o caminho com atraso crítico.

A Figura 2 ilustra um arranjo de transistores, no qual implementou-se diferentes técnicas de dimensionamento. Com o intuito de simplificar o entendimento dos métodos, a Figura 2 possui apenas o N-MOSFET. Pode-se ver a técnica LE na Figura 3(a), a Técnica SP na Figura 3(b) e a Técnica Proposta na Figura 3(c) que estabelece uma assimetria em seu dimensionamento, a fim de obter melhores resultados.

**Figura 2. Implementação de técnicas de dimensionamento em um circuito Pull-Down. Técnica LE (a), Técnica SP (b) e Técnica Proposta (c). Adaptado de: [Kessler et al. 2022a].**

Partindo da premissa de que uma abordagem de dimensionamento assimétrico pode apresentar resultados favoráveis em portas complexas, foi conduzida uma simulação elétrica em uma rede complexa de transistores utilizando a tecnologia de 40nm. Com o intuito de validar os experimentos e identificar um possível nicho para as portas complexas e a assimetria de dimensionamento.

Nesse contexto, o presente trabalho tem como objetivo reimplementar e avaliar os métodos já discutidos na literatura [Kessler et al. 2022a] [Böhlke 2021] [Sutherland et al. 1999] para o dimensionamento de transistores em portas lógicas. Após a obtenção dos resultados, foi proposta uma abordagem metodológica alternativa, focando em modelos assimétricos de dimensionamento, com o objetivo de otimizar as características das portas lógicas complexas.

#### 4. Ambiente de Simulação

Para realizar as simulações elétricas, utilizou-se o SPICE, *Simulation Program with Integrated Circuit Emphasis*, o qual é um programa de simulação de circuitos eletrônicos que permite simular o comportamento de transistores sem a necessidade de fabricá-los.

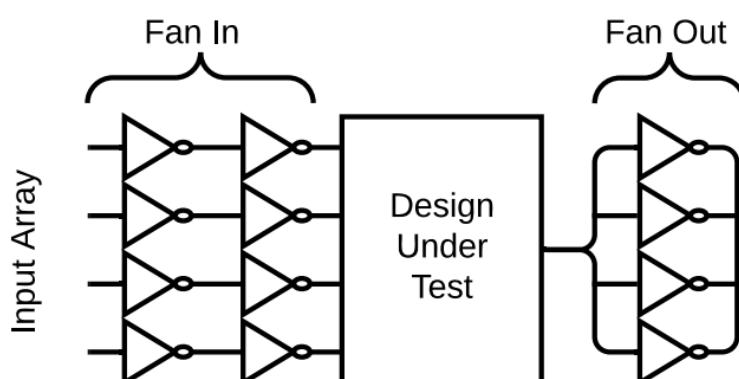

Com o uso do SPICE, primeiramente criou-se o ambiente de simulação onde o *Design Under Test* (DUT) (Design de teste) foi testado. Para isso, os vetores de entrada (*Input Array*) foram conectadas a inversores em série nas entradas do circuito (*Fan In*), a fim de proporcionar um pulso quadrado com um atraso mais realista. Inversores em paralelo foram aplicados na saída do circuito (*Fan Out*), conforme ilustrado na Figura 3. Durante as simulações, a quantidade de inversores em paralelo na saída foram ajustados, permitindo que o dimensionamento fosse realizado para diferentes valores de cargas de saída.

**Figura 3. Ambiente de simulação.** Fonte: [Kessler et al. 2022b].

Dentro do ambiente de simulação, duas fontes de tensão foram criadas: uma para entradas e saídas e outra para o DUT, com o objetivo de obter medidas de potência baseadas na porta lógica simulada. Também foram implementadas fontes modulares para os arcos das matrizes de entrada. Esses arcos são os estímulos necessários para avaliar as características elétricas da porta lógica.

Para o projeto das portas lógicas usadas no SPICE, empregou-se a ferramenta *SwitchCraft* [Callegaro et al. 2010]. Essa ferramenta gera, a partir de uma função lógica, o arranjo de transistores de acordo com a topologia selecionada no SPICE. Também é possível obter o dimensionamento do LE [Sutherland et al. 1999] com esse programa.

Após a implementação dos DUTs, foi feita a construção das variáveis a serem medidas, que incluirão o *Slope* (declive), atraso de propagação e consumo dinâmico de potência. Essas medidas são utilizadas no *Liberty*. O *Slope* é uma forma de medir o atraso do circuito a partir das inclinações da curva da tensão de saída do DUT. Isto envolve comparar um ponto em 20% da rampa com um ponto em 80% de tensão, tanto para subidas quanto para descidas das curvas. O atraso de propagação é o tempo que a saída do circuito demora para responder ao pulso de entrada, medido através do ponto de 50% da rampa de tensão da entrada e da saída, quando ocorre a mudança de nível lógico (circuito conduzindo ou não conduzindo). O consumo dinâmico é a dissipação de potência que ocorre durante as transições de estados do circuito, calculando o produto da corrente elétrica pela tensão do circuito durante a mudança de estado.

Com intuito de automatizar a criação dos arquivos SPICEs para efetuar as simulações, foi criado uma ferramenta que recebe como parâmetros de entrada uma função lógica no formato soma de produtos e um arquivo com o sub-circuito extraído

do *SwitchCraft*. O programa foi feito na linguagem C++ e retorna como saída 49 SPICEs com todo o ambiente de simulação projetado, combinando 7 *Slopes* de entrada com 7 cargas de saída.

Para executar as simulações, o programa gera um arquivo de lote (.bat) que simula os 49 SPICEs e gera os arquivos contendo os valores dos resultados das simulações. A partir dos arquivos de resultados, foi criado um outro programa em C++ para extrair os resultados e colocá-los no formato *Liberty*.

#### 4.1. Especificações das Simulações

Para validar um possível aprofundamento no dimensionamento assimétrico de transistores, o presente trabalho simulou 5 portas lógicas complexas que continham bifurcações em suas redes de transistores, sendo elas:  $(a*b*c*d+a*e*f+a*g)$ ;  $(a*b+a*c*d+e)$ ;  $(a*b+a*c*d+a*c*e)$ ;  $(a*b*c+a*d*e*f+g*h)$ ;  $(a*e*f+a*d+b*c*e*f+b*c*d)$ . O projeto de-las foi extraído a partir do *SwitchCraft* [Callegaro et al. 2010]. As simulações foram feitas utilizando tecnologia MOSFET de 40nm.

As simulações foram feitas utilizando as técnicas LE, SP e a técnica proposta de dimensionamento assimétrico. O foco destes experimentos foram de comparar atraso de propagação, *Slope* e potência dinâmica dos transistores, utilizando cargas de saídas de 4,32 e 128 inversores, com o objetivo de avaliar o comportamento das técnicas de dimensionamento para diferentes situações.

### 5. Resultados e Discussão

Os resultados obtidos nas simulações foram comparados com as técnicas de dimensionamento LE [Sutherland et al. 1999] e SP [Böhlke 2021]. Utilizou-se as cargas de 4,32 e 128 inversores e os resultados foram normalizados em função da técnica LE, mostrando o consumo e a potência das 5 portas lógicas simuladas.

A Tabela 1 mostra os resultados para uma carga pequena de 4 inversores. Pode-se notar que a técnica SP oferece os melhores resultados de consumo de potência, enquanto a técnica proposta, no geral, não obteve resultados muito bons.

**Tabela 1. Simulação da Carga de Saída de 4 Inversores**

| Porta Lógica | Métrica         | FO4    |        |          |

|--------------|-----------------|--------|--------|----------|

|              |                 | LE     | SP     | Proposta |

| Porta 1      | <b>Atraso</b>   | 1,0000 | 1,0156 | 0,9653   |

|              | <b>Slope</b>    | 1,0000 | 1,0070 | 1,0707   |

|              | <b>Potência</b> | 1,0000 | 0,7049 | 0,9540   |

| Porta 2      | <b>Atraso</b>   | 1,0000 | 1,0093 | 1,3205   |

|              | <b>Slope</b>    | 1,0000 | 0,9182 | 0,9662   |

|              | <b>Potência</b> | 1,0000 | 0,7536 | 0,9555   |

| Porta 3      | <b>Atraso</b>   | 1,0000 | 0,9570 | 1,1926   |

|              | <b>Slope</b>    | 1,0000 | 1,0155 | 1,0899   |

|              | <b>Potência</b> | 1,0000 | 0,7127 | 0,9630   |

| Porta 4      | <b>Atraso</b>   | 1,0000 | 0,9999 | 1,3709   |

|              | <b>Slope</b>    | 1,0000 | 0,9668 | 0,9796   |

|              | <b>Potência</b> | 1,0000 | 0,6782 | 0,9752   |

| Porta 5      | <b>Atraso</b>   | 1,0000 | 1,0008 | 0,9561   |

|              | <b>Slope</b>    | 1,0000 | 1,0325 | 1,1769   |

|              | <b>Potência</b> | 1,0000 | 0,7152 | 0,9237   |

A Tabela 2 mostra os resultados para uma carga média de 32 inversores, assim como na carga pequena, a técnica SP obteve os melhores resultados de potência, porém, a técnica proposta obteve resultados satisfatórios de atraso de propagação e *Slope*.

**Tabela 2. Simulação da Carga de Saída de 32 inversores**

| Porta Lógica | Métrica  | FO32   |        |          |

|--------------|----------|--------|--------|----------|

|              |          | LE     | SP     | Proposta |

| Porta 1      | Atraso   | 1,0000 | 1,0055 | 0,9830   |

|              | Slope    | 1,0000 | 1,0031 | 0,9978   |

|              | Potência | 1,0000 | 0,8837 | 0,9818   |

| Porta 2      | Atraso   | 1,0000 | 0,9911 | 0,9761   |

|              | Slope    | 1,0000 | 1,0022 | 0,9987   |

|              | Potência | 1,0000 | 0,9180 | 0,9851   |

| Porta 3      | Atraso   | 1,0000 | 0,9824 | 0,9843   |

|              | Slope    | 1,0000 | 1,0020 | 0,9986   |

|              | Potência | 1,0000 | 0,8949 | 0,9863   |

| Porta 4      | Atraso   | 1,0000 | 0,9898 | 1,0571   |

|              | Slope    | 1,0000 | 0,9880 | 0,9987   |

|              | Potência | 1,0000 | 0,8667 | 0,9895   |

| Porta 5      | Atraso   | 1,0000 | 0,9904 | 1,0452   |

|              | Slope    | 1,0000 | 1,0026 | 1,0108   |

|              | Potência | 1,0000 | 0,8973 | 0,9724   |

Por último, a Tabela 3 mostra os resultados para uma carga alta de 128 inversores, onde pode-se observar que os resultados ficaram muito próximos aos dos de 32 inversores. Acredita-se que essas alterações no dimensionamento impactam na capacidade parasita do circuito, fazendo com que conforme se aumenta a carga, em um determinado momento os ganhos estabilizem.

**Tabela 3. Simulação da Carga de Saída de 128 inversores**

| Porta Lógica | Métrica  | FO128  |        |          |

|--------------|----------|--------|--------|----------|

|              |          | LE     | SP     | Proposta |

| Porta 1      | Atraso   | 1,0000 | 1,0019 | 0,9940   |

|              | Slope    | 1,0000 | 1,0005 | 1,0000   |

|              | Potência | 1,0000 | 0,9553 | 0,9888   |

| Porta 2      | Atraso   | 1,0000 | 0,9970 | 0,9922   |

|              | Slope    | 1,0000 | 1,0004 | 0,9998   |

|              | Potência | 1,0000 | 0,9777 | 0,9941   |

| Porta 3      | Atraso   | 1,0000 | 0,9941 | 0,9947   |

|              | Slope    | 1,0000 | 1,0004 | 0,9998   |

|              | Potência | 1,0000 | 0,9637 | 0,9920   |

| Porta 4      | Atraso   | 1,0000 | 0,9961 | 0,9922   |

|              | Slope    | 1,0000 | 1,0005 | 0,9997   |

|              | Potência | 1,0000 | 0,9502 | 0,9958   |

| Porta 5      | Atraso   | 1,0000 | 0,9967 | 1,0144   |

|              | Slope    | 1,0000 | 1,0006 | 1,0000   |

|              | Potência | 1,0000 | 0,9640 | 0,9751   |

Em termos gerais, a técnica que foi proposta demonstrou melhorias no atraso de propagação. No entanto, em cenários específicos, notou-se um aumento no atraso de propagação. Isso ocorreu porque, nesses casos, o caminho que teve seu dimensionamento reduzido pela aplicação da técnica tornou-se o caminho crítico. A Tabela 4 mostra uma simplificação dos resultados, a qual possui o valor médio dos resultados das 5 portas,

onde observa-se que conforme se aumenta a carga de saída, a técnica proposta apresenta resultados mais eficientes.

**Tabela 4. Média das portas simuladas**

| Porta Lógica | Métrica         | Média das Portas |        |          |

|--------------|-----------------|------------------|--------|----------|

|              |                 | LE               | SP     | Proposta |

| FO4          | <b>Atraso</b>   | 1,0000           | 0,9965 | 1,1611   |

|              | <b>Slope</b>    | 1,0000           | 0,9769 | 1,0266   |

|              | <b>Potência</b> | 1,0000           | 0,7129 | 0,9543   |

| FO32         | <b>Atraso</b>   | 1,0000           | 0,9918 | 1,0091   |

|              | <b>Slope</b>    | 1,0000           | 0,9988 | 0,9984   |

|              | <b>Potência</b> | 1,0000           | 0,8921 | 0,9830   |

| FO128        | <b>Atraso</b>   | 1,0000           | 0,9972 | 0,9975   |

|              | <b>Slope</b>    | 1,0000           | 1,0004 | 0,9998   |

|              | <b>Potência</b> | 1,0000           | 0,9622 | 0,9892   |

Para preservar o atraso crítico das portas lógicas, é crucial aprimorar a técnica assimétrica de dimensionamento de transistores, a fim de evitar a redução do dimensionamento no caminho crítico. Um exemplo disso pode ser visto na porta 5, onde o aumento da carga de saída resultou em uma piora no atraso de propagação. Nesse caso, o caminho crítico do circuito foi afetado pela técnica assimétrica, levando a perdas nos resultados e destacando a necessidade de aprimorar essa abordagem.

Com base nos resultados obtidos, também é possível observar a consistência das técnicas em relação ao consumo de potência. Em todos os casos, a técnica SP se destacou com os melhores resultados, enquanto a técnica LE apresentou os piores desempenhos. Além disso, em muitos cenários com cargas médias e altas, a técnica proposta demonstrou melhorias significativas no *Slope* e no atraso de propagação.

## 6. Conclusões e Trabalhos Futuros

Com os experimentos realizados, pode-se dizer que uma técnica assimétrica de dimensionamento de transistores em portas complexas pode oferecer resultados promissores, quando comparadas a outras abordagens, principalmente para cargas maiores e com ênfase no atraso de propagação. A técnica ainda se encontra em desenvolvimento e, com base nesses resultados, tem como objetivo buscar otimizações para que também obtenha bons resultados de atraso de propagação para cargas pequenas.

Nas fases posteriores do projeto de portas lógicas, como o leiaute, a abordagem assimétrica não acrescenta complexidade em comparação com o LE. Isso ocorre devido o dimensionamento resultante ser sempre igual ou menor do que o obtido com o LE. Em alguns casos, a área do circuito pode ser reduzida, uma vez que as alterações nos dimensionamentos podem eliminar a necessidade de técnicas de leiaute, como o *Folding*, que poderia ser necessário em situações específicas.

Para trabalhos futuros, será simulada uma maior quantidade de portas lógicas complexas visando encontrar algum padrão, afim de aperfeiçoar a técnica assimétrica e saber

com mais precisão para quais tipos de cargas e redes de transistores esta técnica pode trazer benefícios. Neste trabalho os resultados foram tabelados de maneira simples e abstrata, futuramente pretende-se criar um *script* que leia e compare arquivos *Liberty* de diferentes portas lógicas na tentativa de buscar um padrão de dimensionamento assimétrico.

## Referências

- Böhlke, M. S. (2021). Adaptação ao logical effort: Mantendo a simplicidade e reduzindo o consumo em portas complexas. Trabalho de Conclusão de Curso. Universidade Federal de Pelotas.

- Callegaro, V., Marques, F. d. S., Klock, C. E., da Rosa Jr, L. S., Ribas, R. P., and Reis, A. I. (2010). Switchcraft: a framework for transistor network design. In *Proceedings of the 23rd symposium on Integrated circuits and system design*, pages 49–53.

- Kessler, H., Bohlke, M., da Rosa, L. S., Porto, M., and Camargo, V. V. (2022a). Calibration of logical effort transistor sizing for on-the-fly low-power supergate design. In *2022 IEEE 13th Latin America Symposium on Circuits and System (LASCAS)*, pages 1–4. IEEE.

- Kessler, H., Porto, M., Da Rosa, L., and Camargo, V. V. (2022b). Standard cell and supergates designs: An electrical comparison on 4-input logic functions. In *2022 IEEE International Symposium on Circuits and Systems (ISCAS)*, pages 1744–1748. IEEE.

- Kessler, H. C. (2022). Static cmos complex gates: electrical investigation of design strategies. Master's thesis, Universidade Federal de Pelotas.

- Kofuji, S. T., Zuffo, J. A., and Soares, J. N. (1990). Circuitos integrados cmos. *Disciplina de Eletrônica Experimental*.

- Marques, F. S., Rosa Jr, L., Ribas, R. P., Sapatnekar, S. S., and Reis, A. I. (2007). Dag based library-free technology mapping. In *Proceedings of the 17th ACM Great Lakes symposium on VLSI*, pages 293–298.

- Moore, G. (1965). Moore's law. *Electronics Magazine*, 38(8):114.

- Ricci, A., De Munari, I., and Ciampolini, P. (2007). An evolutionary approach for standard-cell library reduction. In *Proceedings of the 17th ACM Great Lakes symposium on VLSI*, pages 305–310.

- Sutherland, I., Sproull, R. F., and Harris, D. (1999). *Logical effort: designing fast CMOS circuits*. Morgan Kaufmann.

- Tseng, I., Postula, A., and Jozwiak, L. (2005). Symbolic extraction for estimating analog layout parasitics in layout-aware synthesis.

- Weste, N. and Harris, D. (2011). *CMOS VLSI Design: A Circuits and Systems Perspective*. Pearson Education.